Nand flash

LUN → CE → Die → Plane → Bank → Block → Page

- Block 是擦除操作的最小单位

- Page 是读写操作的最小单位,常见的Nand Flash多数是2KB,最新的是4KB、8KB

- 硬件电路只支持 “一次性操作一个 Page 的所有单元”,因此读写必须以 Page 为单位。

- 写入前必须先擦除对应的Block

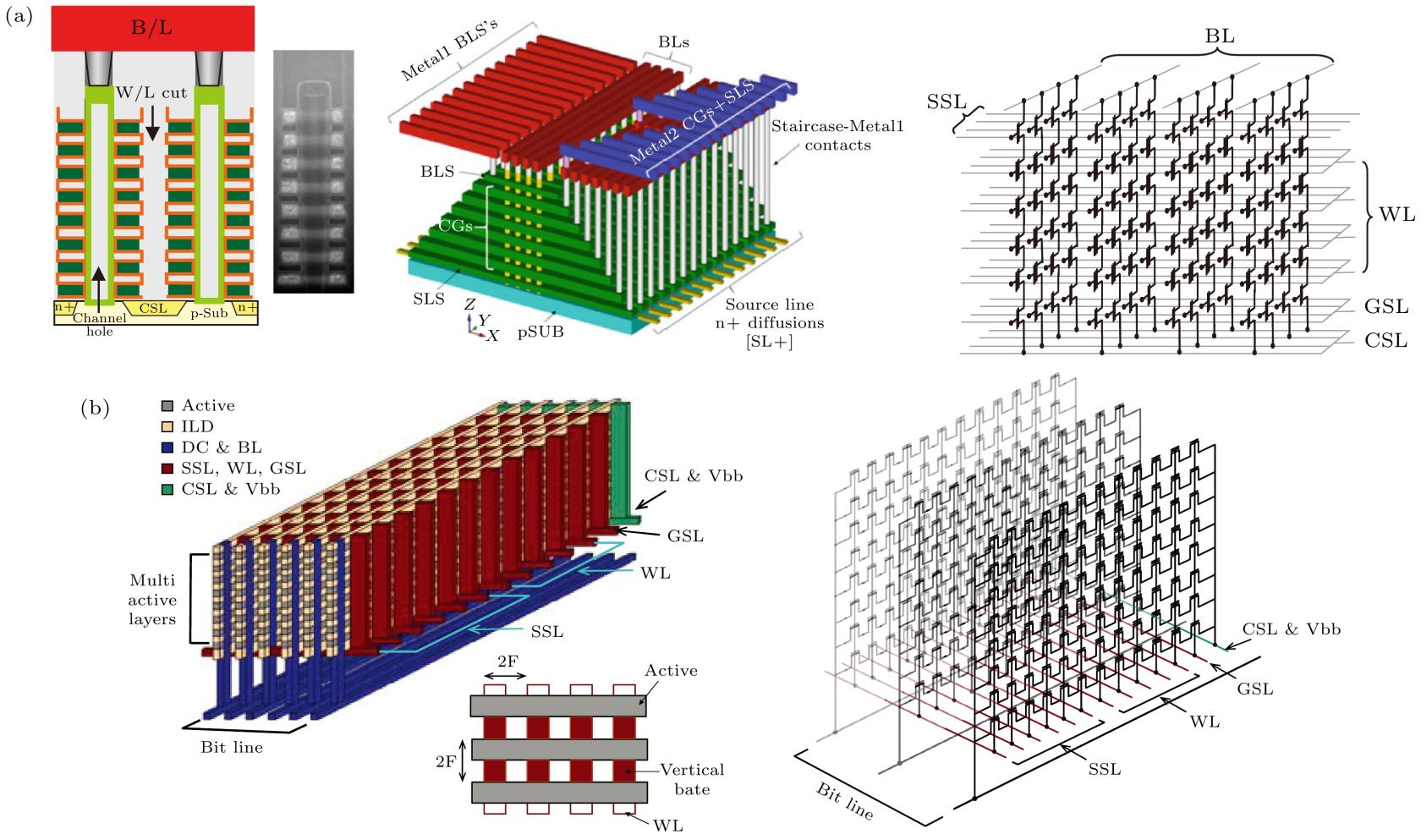

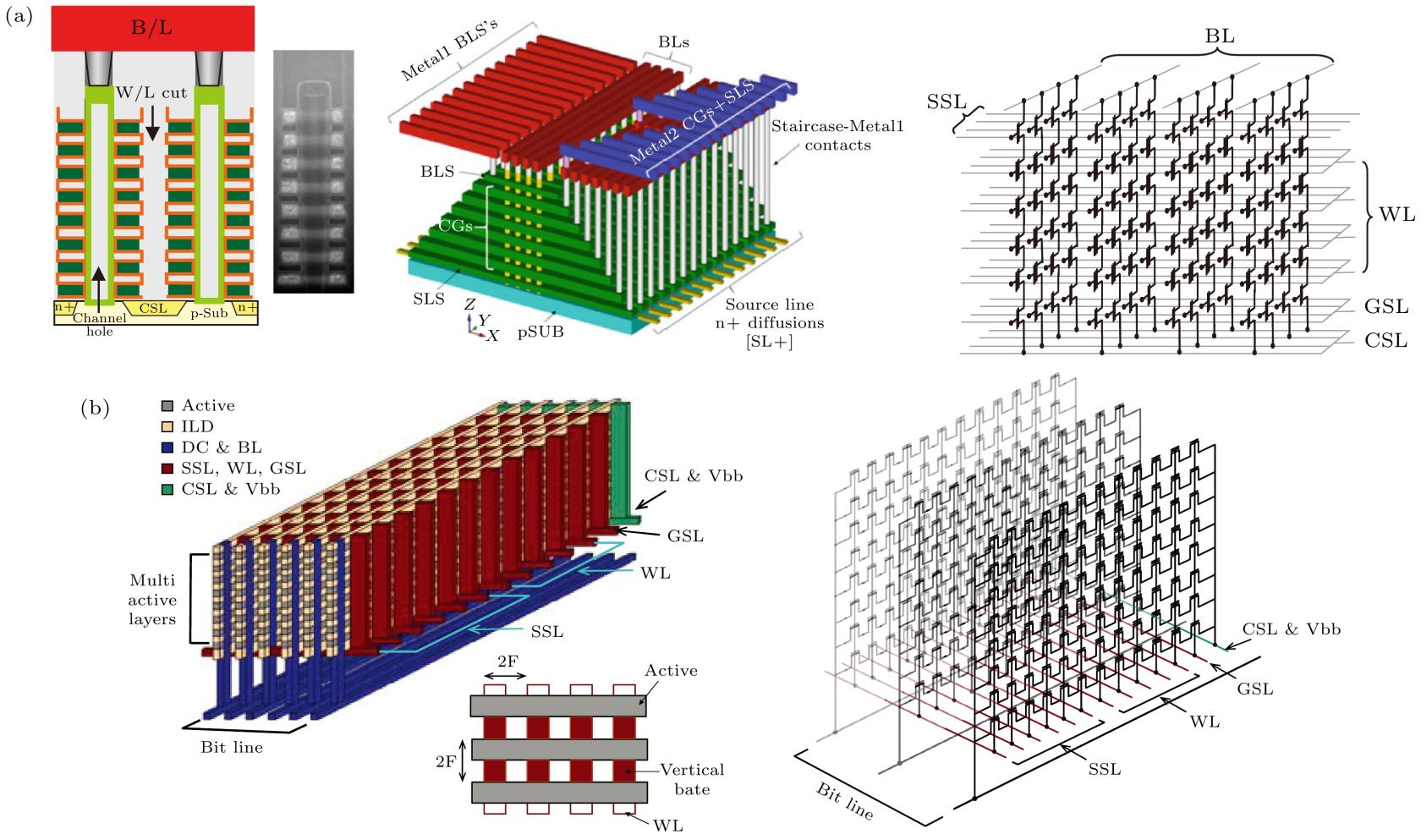

- 栅极堆叠(Gate-Stacked) 和沟道堆叠(Channel-Stacked)两种结构均需解决 “垂直互联”,如何连接不同层的字线 WL 和位线 BL

- 位置:WL 是平行于浮栅晶体管控制栅的金属或多晶硅连线,贯穿整个存储阵列的行方向(类似 “横线”)。

- 连接方式:同一行(Row)中所有浮栅晶体管的控制栅都与同一条 WL 相连。一个 Page 内的所有存储单元通常属于同一行,共享一条 WL。

- 写入:向 WL 施加高电压(如 10-20V),通过 “热电子注入” 或 “F-N 隧穿效应”,将电子注入浮栅(存储 “0”)。

- 读取:向 WL 施加中等电压(如 2-5V),根据晶体管是否导通判断浮栅是否带电荷(即区分 “0” 和 “1”)。

- 擦除:擦除操作针对整个 Block(块),此时 WL 接地,衬底施加高电压,通过 F-N 隧穿效应让浮栅释放电荷(恢复为 “1”)。

- 位置:BL 是垂直于 WL 的金属连线,沿存储阵列的列方向延伸(类似 “竖线”)。

- 连接方式:同一列(Column)中所有浮栅晶体管的漏极通过接触孔(Contact)与同一条 BL 相连。

- 材料:通常采用铝或铜,以降低连线电阻,提高信号传输速度。

- BL 是数据信号的 “传输通道”,负责将存储单元的状态(导通 / 截止)转化为电信号并传递给外部电路

- 一条 BL 对应一列存储单元,每列中的每个单元对应一个 “位”(bit)

SSL(,)